CS5460/6460: Operating Systems

Lecture 14: Scalability techniques

Anton Burtsev February, 2014

## Recap: read and write barriers

```

void bar(void)

void foo(void)

while (b == 0)

a = 1;

continue;

smp_wmb();

smp_rmb();

b = 1;

assert(a == 1);

```

```

scheduler(void)

Where is the barrier?

for(;;) {

acquire(&ptable.lock);

for(p = ptable.proc; p < &ptable.proc[NPROC]; p++)</pre>

{

if(p->state != RUNNABLE)

continue;

p->state = RUNNING;

swtch(&cpu->scheduler, proc->context);

}

release(&ptable.lock);

}

```

# Scalable spinlocks

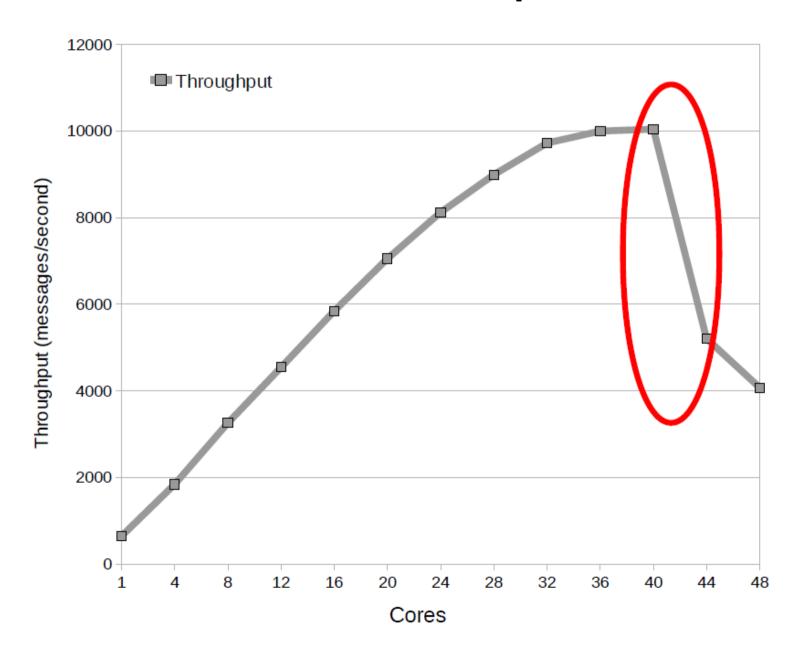

# Exim collapse

## Spinlock collapse

- We discussed two solutions:

- Per-core hash-table

- Read copy update

Is it possible to build scalable spinlocks?

```

struct qnode {

MCS lock

volatile void *next;

volatile char locked;

};

typedef struct {

struct qnode *v;

} mcslock_t;

arch_mcs_lock(mcslock_t *1, volatile struct qnode *mynode) {

struct qnode *predecessor;

mynode->next = NULL;

predecessor = (struct qnode *)xchg((long *)&l->v, (long)mynode);

if (predecessor) {

mynode->locked = 1;

barrier();

predecessor->next = mynode;

while (mynode->locked) ;

```

```

arch mcs lock(mcslock t *1, volatile struct gnode *mynode) {

unlock

struct qnode *predecessor;

mynode->next = NULL;

predecessor = (struct qnode *)xchg((long *)&l->v, (long)mynode);

if (predecessor) {

mynode->locked = 1;

barrier();

predecessor->next = mynode;

while (mynode->locked) ;

}

}

arch mcs unlock(mcslock t *1, volatile struct qnode *mynode) {

if (!mynode->next) {

if (cmpxchg((long *)&l->v, (long)mynode, 0) == (long)mynode)

return;

while (!mynode->next);

((struct qnode *)mynode->next)->locked = 0;

```

## Why does this scale?

## Ticket spinlock

```

void spin_lock(spinlock_t *lock)

{

t = atomic_inc(lock->next_ticket);

while (t != lock->current_ticket)

; /* Spin */

}

struct spinlock(spinlock_t *lock)

{

lock->current_ticket++;

}

struct spinlock_t {

int current_ticket;

int next_ticket;

}

```

How many cache messages are needed to acquire the lock?

## Ticket spinlock

```

void spin_lock(spinlock_t *lock)

{

t = atomic_inc(lock->next_ticket);

while (t != lock->current_ticket)

; /* Spin */

}

struct spinlock(spinlock_t *lock)

{

lock->current_ticket++;

}

struct spinlock_t {

int current_ticket;

int next_ticket;

}

```

- How many cache messages are needed to acquire the lock?

- Proportional to the number of cores

- 1 message for atomic\_inc()

- N messages from other cores which hold the lock and update current ticket upon release

```

arch mcs lock(mcslock t *1, volatile struct qnode *mynode) {

struct qnode *predecessor;

mynode->next = NULL;

predecessor = (struct qnode *)xchg((long *)&l->v, (long)mynode);

if (predecessor) {

mynode->locked = 1;

Constant number of

barrier();

cache coherence

predecessor->next = mynode;

messages

while (mynode->locked) ;

}

}

arch mcs unlock(mcslock t *1, volatile struct qnode *mynode) {

if (!mynode->next) {

if (cmpxchg((long *)\&l->v, (long)mynode, 0) == (long)mynode)

return;

while (!mynode->next) ;

((struct gnode *)mynode->next)->locked = 0;

```

#### Cache line isolation

```

struct qnode {

volatile void *next;

volatile char locked;

char __pad[0] __attribute__((aligned(64)));

};

typedef struct {

struct qnode *v __attribute__((aligned(64)));

} mcslock_t;

```

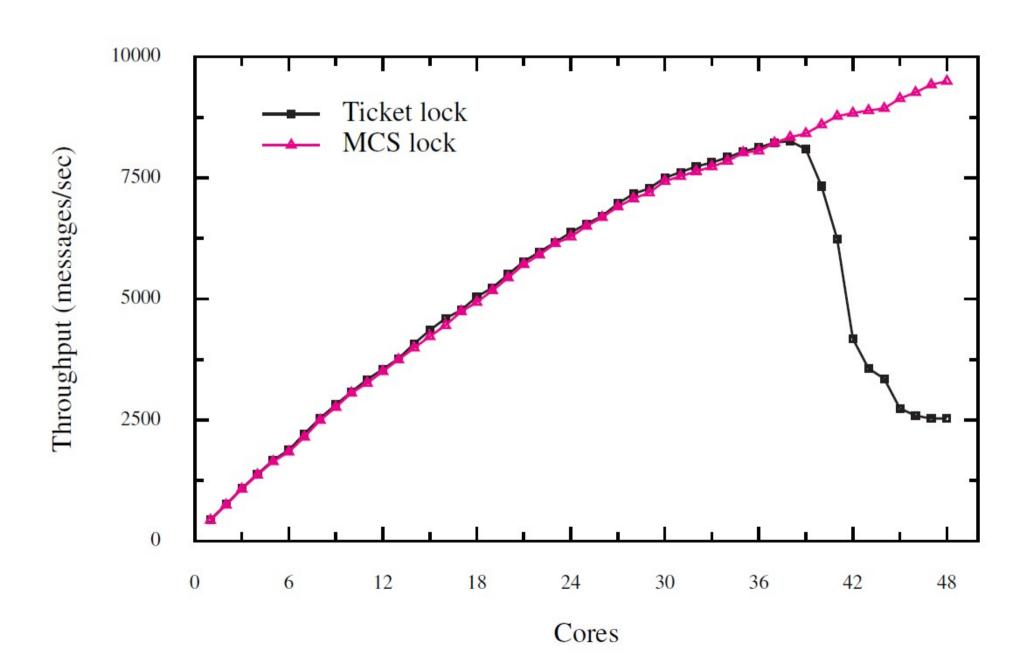

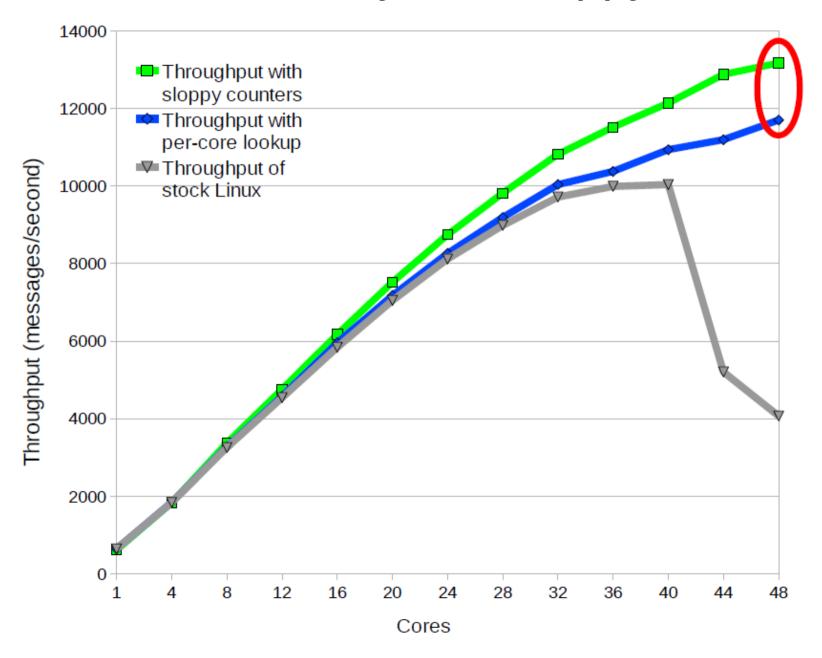

## Exim: MCS vs ticket lock

# Hardware transactional memory

```

9 insert(int data)

10 {

11 struct list *1;

13 \quad l = malloc(size of *l);

14 \quad 1-> data = data;

15 l \rightarrow next = list;

16 list = 1;

17 }

```

Original list

implementation

```

9 insert(int data)

We protected list

10 {

with locks

struct list *1;

11

13 \quad l = malloc(size of *l);

14 \quad 1-> data = data;

acquire(&listlock);

15

l->next = list;

16 list = 1;

release(&listlock);

17 }

```

```

9 insert(int data)

Hardware

10 {

transaction

11

struct list *1;

13 \quad l = malloc(size of *l);

14 \quad 1-> data = data;

15

1->next = list;

Writes cached

locally

16

list = 1;

Atomic

transaction

17 }

CPU cache

```

# Intel Transactional Synchronization Extensions (TSX)

- Two modes of execution

- Restricted transactional memory (RTM)

- Hardware lock elision (HLE)

## Restricted transactional memory

```

_retry: xbegin _abort

// critical section

xend

abort:

// Fallback path, retry

// transaction or acquire a lock

```

## Restricted transactional memory

- Some instructions and events may cause aborts

- Uncommon instructions, interrupts, faults

- Software must provide non-transactional path

#### Hardware lock elision

- Is it possible to use transactional memory without changing the code?

- Hint: use existing locks as hints for transactions

#### Hardware lock elision

```

mov eax, 1

_try: xacquire lock xchg lock, eax

cmp eax, 0

jz _success

_spin: pause

cmp lock, 1

jz _spin

jmp _try

// critical section

xrelease mov lock, 0

```

### Hardware lock elision

- Try to execute lock code in the transactional manner

- In case of abort, do a transparent restart

- Execute same software code without elision

## Scalable commutativity rule

## Thinking about scalability

- Scalability is typically viewed as a property of implementation

- Is it possible to detect scalability bottlenecks at the level of interfaces

Whenever interface operations commute, they can be implemented in a way that scales

## Designing commutative interfaces

- Decompose compound operations

- fork()

- Creates a new process and snapshots its entire memory, file descriptors, signal masks

- Fails to commute with memory writes, address space operations, and many file descriptor operations

- stat()

- Retrieves many stats simultaneously

- Fails to commute with any operation that changes any attribute returned by stat, e.g., link, chmod, chown, write, and even read

## Designing commutative interfaces (2)

- Embrace specification non-determinism

- Lowest available file-descriptor

- Permit weak ordering

- Local domain sockets

- send and receive operations do not commute

- Unnecessary in case of multiple readers and writers

- Release resources asynchronously

- munmap requires expensive TLB shootdowns before it can return

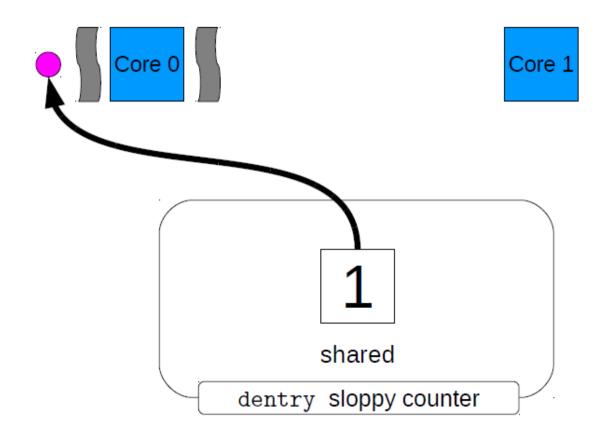

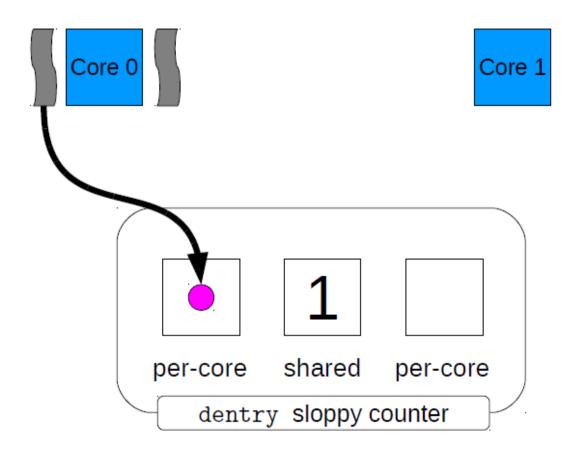

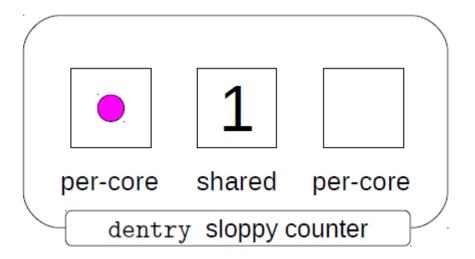

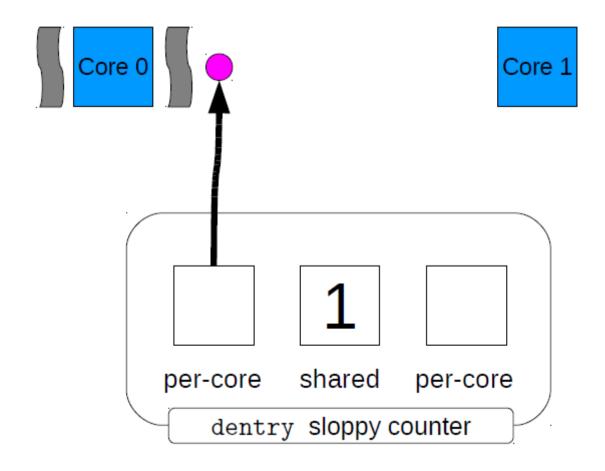

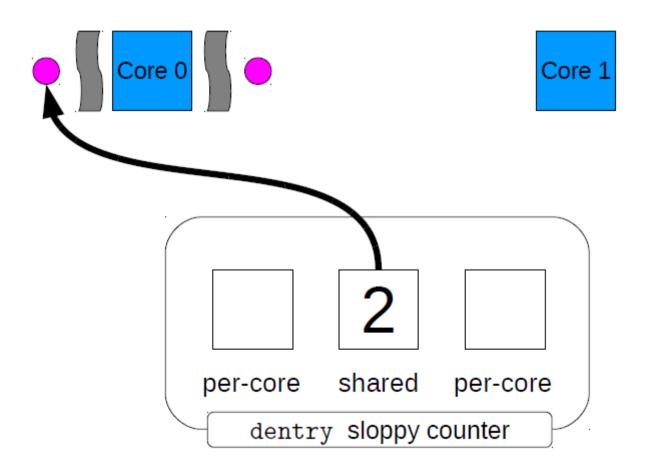

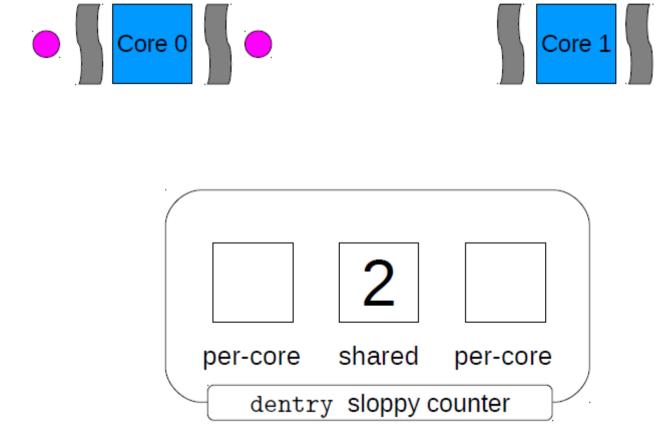

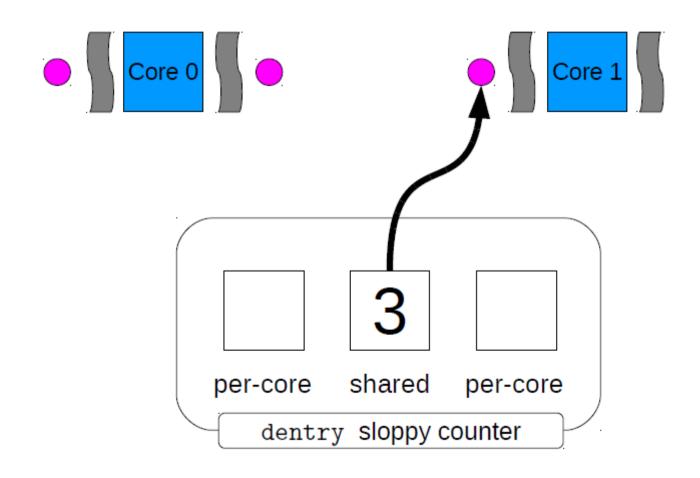

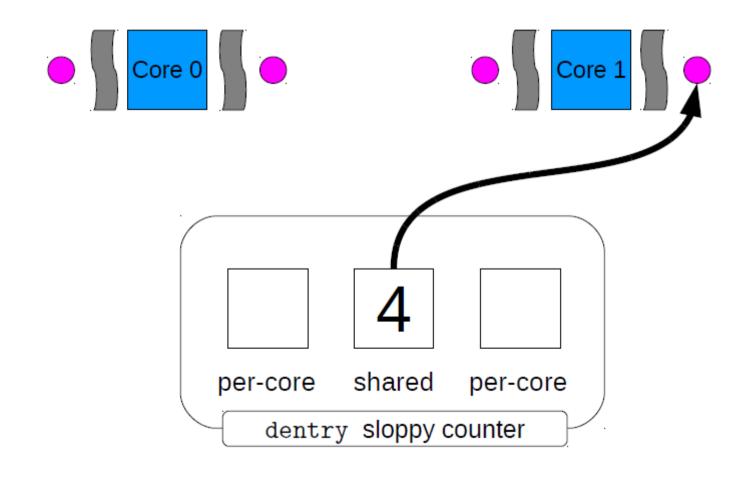

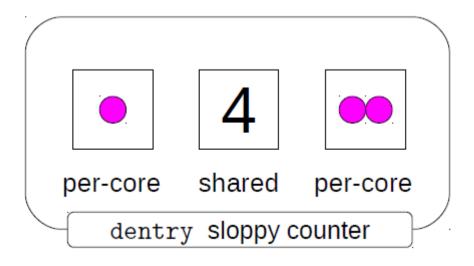

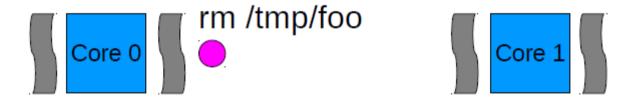

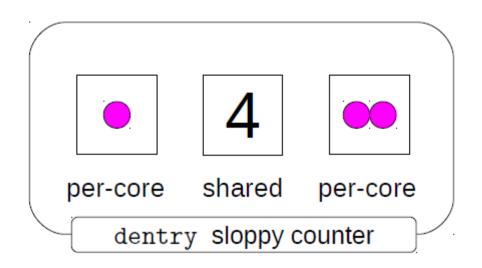

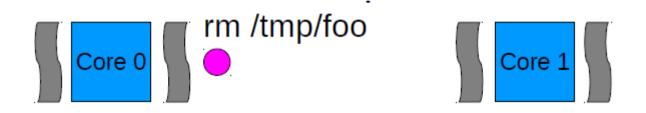

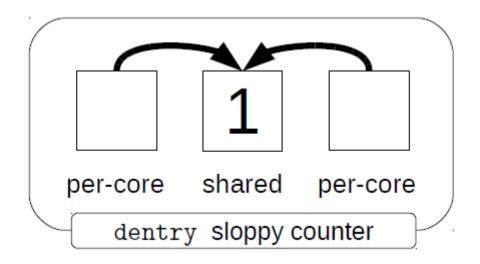

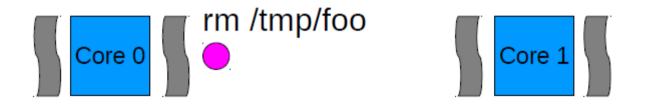

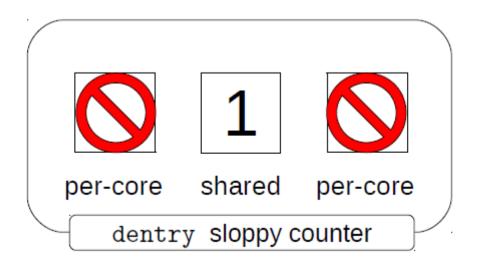

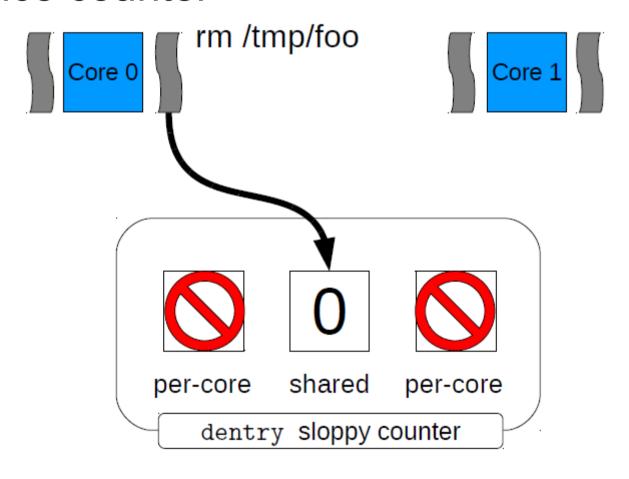

# One more scalability technique: sloppy counters

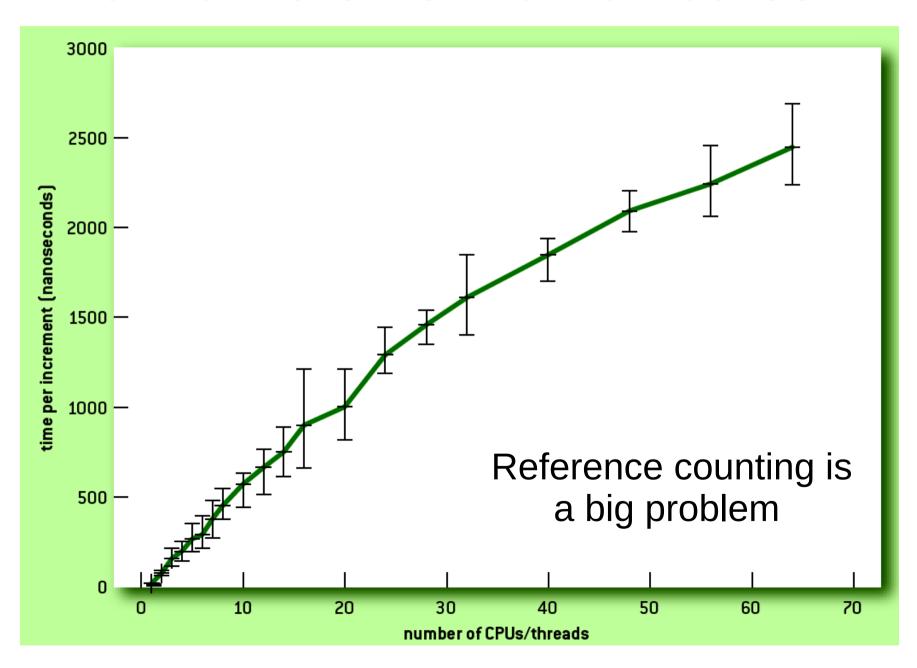

## Reference counting

- Reference counting is used to keep track of object users

- Increment counter for every new user

- Decrement counter when users leave

- Deallocate object when counter is 0, e.g. there are no users

### Atomic increment on 64 cores

Observation: kernel rarely needs true value of a reference counter

Observation: kernel rarely needs true value of a reference counter

Observation: kernel rarely needs true value of a reference counter

Observation: kernel rarely needs true value of a reference counter

#### Exim: more scalability with sloppy counters

#### Conclusion

# Thank you!