# CACHE ARCHITECTURE

Mahdi Nazm Bojnordi

Assistant Professor

School of Computing

University of Utah

THE

OF UTAH

CS/ECE 6810: Computer Architecture UNIVERSITY

#### Announcement

Homework 4 will be released on Oct. 30<sup>th</sup>

#### This lecture

- Cache addressing and lookup

- Cache optimizations

- Techniques to improve miss rate

- Replacement policies

- Write policies

How to improve cache performance?

AMAT = t<sub>h</sub> + r<sub>m</sub> t<sub>p</sub>

Reduce hit time (t<sub>h</sub>)

$\Box$  Improve hit rate (1 -  $r_m$ )

$\Box$  Reduce miss penalty (t<sub>p</sub>)

□ How to improve cache performance?

$$AMAT = t_h + r_m t_p$$

$\square$  Reduce hit time (t<sub>h</sub>)

Memory technology, critical access path

- $\square$  Improve hit rate (1  $r_m$ )

- $\Box$  Reduce miss penalty (t<sub>p</sub>)

How to improve cache performance?

$$AMAT = t_h + r_m t_p$$

$\square$  Reduce hit time (t<sub>h</sub>)

Memory technology, critical access path

$\square$  Improve hit rate (1 -  $r_m$ )

Size, associativity, placement/replacement policies

$\Box$  Reduce miss penalty (t<sub>p</sub>)

How to improve cache performance?

$$AMAT = t_h + r_m t_p$$

$\square$  Reduce hit time (t<sub>h</sub>)

Memory technology, critical access path

$\Box$  Improve hit rate (1 -  $r_m$ )

Size, associativity, placement/replacement policies

$\Box$  Reduce miss penalty (t<sub>p</sub>)

Multi level caches, data prefetching

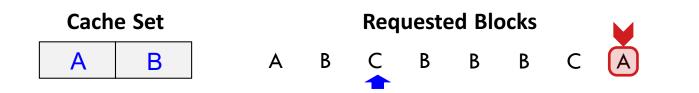

## Set Associative Caches

- Improve cache hit rate by allowing a memory location to be placed in more than one cache block

- N-way set associative cache

- Fully associative

- For fixed capacity, higher associativity typically leads to higher hit rates

- more places to simultaneously map cache lines

- 8-way SA close to FA in practice

## Set Associative Caches

- Improve cache hit rate by allowing a memory location to be placed in more than one cache block

- N-way set associative cache

- Fully associative

- For fixed capacity, higher associativity typically leads to higher hit rates

- more places to simultaneously map cache lines

- 8-way SA close to FA in practice

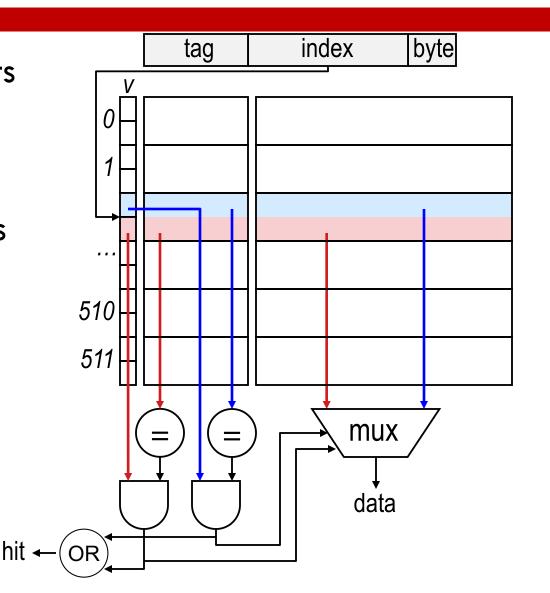

## n-Way Set Associative Lookup

- Index into cache sets

- Multiple tag

comparisons

- Multiple data reads

- Special cases

- Direct mapped

- Single block sets

- Fully associative

- Single set cache

#### **Example Problem**

Find the size of tag, index, and offset bits for an 4MB, 4-way set associative cache with 32B cache blocks. Assume that the processor can address up to 4GB of main memory.

#### **Example Problem**

- Find the size of tag, index, and offset bits for an 4MB, 4-way set associative cache with 32B cache blocks. Assume that the processor can address up to 4GB of main memory.

- $\Box 4GB = 2^{32} B \rightarrow address bits = 32$

- $\square$  32B = 2<sup>5</sup> B  $\rightarrow$  byte offset bits = 5

- $\square 4MB/(4x32B) = 2^{15} \rightarrow index bits = 15$

- $\Box$  tag bits = 32 5 15 = 12

Start by measuring miss rate with an ideal cache

1. ideal is fully associative and infinite capacity

2. then reduce capacity to size of interest

3. then reduce associativity to degree of interest

Start by measuring miss rate with an ideal cache

1. ideal is fully associative and infinite capacity

2. then reduce capacity to size of interest

3. then reduce associativity to degree of interest

1. Cold (compulsory)

Start by measuring miss rate with an ideal cache

1. ideal is fully associative and infinite capacity

2. then reduce capacity to size of interest

3. then reduce associativity to degree of interest

1. Cold (compulsory)

Cold start: first access to block

How to improve

large blocks

prefetching

Start by measuring miss rate with an ideal cache

1. ideal is fully associative and infinite capacity

2. then reduce capacity to size of interest

3. then reduce associativity to degree of interest

1. Cold (compulsory)

2. Capacity

Cold start: first access to block

How to improve

large blocks

prefetching

Start by measuring miss rate with an ideal cache

1. ideal is fully associative and infinite capacity

2. then reduce capacity to size of interest

3. then reduce associativity to degree of interest

Cold start: first access to block

How to improve

large blocks

prefetching

1. Cold (compulsory)

2. Capacity

Cache is smaller than the program data

How to improve

large cache

Start by measuring miss rate with an ideal cache

1. ideal is fully associative and infinite capacity

2. then reduce capacity to size of interest

3. then reduce associativity to degree of interest

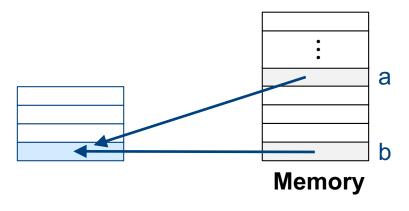

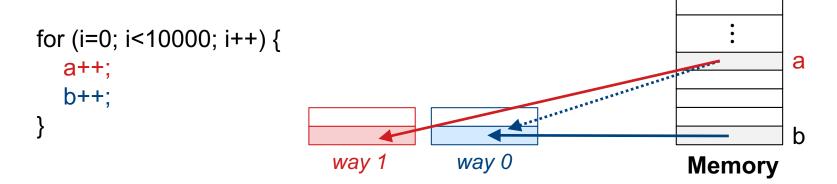

| 1. Cold (compulsory)                                                                                                     | 2. Capacity                                                                                                     | 3. Conflict |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------|

| <ul> <li>Cold start: first access to block</li> <li>How to improve</li> <li>large blocks</li> <li>prefetching</li> </ul> | <ul> <li>Cache is smaller<br/>than the program<br/>data</li> <li>How to improve</li> <li>large cache</li> </ul> |             |

Start by measuring miss rate with an ideal cache

1. ideal is fully associative and infinite capacity

2. then reduce capacity to size of interest

3. then reduce associativity to degree of interest

3. Conflict 1. Cold (compulsory) 2. Capacity Cache is smaller Set size is smaller Cold start: first than the program than mapped access to block How to improve mem. locations data How to improve How to improve large blocks ○ prefetching ○ large cache ○ large cache more assoc.

#### Miss Rates: Example Problem

100,000 loads and stores are generated; L1 cache has 3,000 misses; L2 cache has 1,500 misses. What are various miss rates?

#### Miss Rates: Example Problem

100,000 loads and stores are generated; L1 cache has 3,000 misses; L2 cache has 1,500 misses. What are various miss rates?

- L1 miss rates

- Local/global: 3,000/100,000 = 3%

- L2 miss rates

- □ Local: 1,500/3,000 = 50%

**Global:** 1,500/100,000 = 1.5%

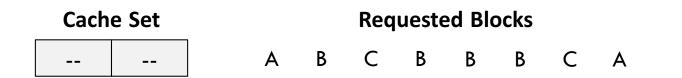

## **Cache Replacement Policies**

- □ Which block to replace on a miss?

- Only one candidate in direct-mapped cache

- Multiple candidates in set/fully associative cache

## **Cache Replacement Policies**

- Which block to replace on a miss?

- Only one candidate in direct-mapped cache

Multiple candidates in set/fully associative cache

Ideal replacement (Belady's algorithm)

Replace the block accessed farthest in the future

## **Cache Replacement Policies**

- Which block to replace on a miss?

- Only one candidate in direct-mapped cache

Multiple candidates in set/fully associative cache

Ideal replacement (Belady's algorithm)

Replace the block accessed farthest in the future