# QUANTIFYING THE IMPACT OF INTERBLOCK WIRE-DELAYS ON PROCESSOR PERFORMANCE

by

Vivek Venkatesan

A thesis submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Master of Science

in

Computer Science

School of Computing

The University of Utah

May 2008

Copyright ©Vivek Venkatesan 2008

All Rights Reserved

### THE UNIVERSITY OF UTAH GRADUATE SCHOOL

# SUPERVISORY COMMITTEE APPROVAL

of a thesis submitted by

Vivek Venkatesan

This thesis has been read by each member of the following supervisory committee and by majority vote has been found to be satisfactory.

Chair: Rajeev Balasubramonian

John B Carter

Ganesh Gopalakrishnan

## THE UNIVERSITY OF UTAH GRADUATE SCHOOL

# FINAL READING APPROVAL

To the Graduate Council of the University of Utah:

I have read the thesis of <u>Vivek Venkatesan</u> in its final form and have found that (1) its format, citations, and bibliographic style are consistent and acceptable; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the Supervisory Committee and is ready for submission to The Graduate School.

Date

Rajeev Balasubramonian Chair, Supervisory Committee

Approved for the Major Department

Martin Berzins Chair/Dean

Approved for the Graduate Council

David S. Chapman Dean of The Graduate School

## ABSTRACT

As logic delays continue to decrease with smaller process technology, on-chip wire delays are growing exponentially and are expected to increase cross-chip communication latencies to tens of cycles. In this work, we quantify the performance impact of wire-delays in three important contexts: (i) within an aggressive outof-order (OoO) processor pipeline on a two-dimensional (2D) plane, (ii) within a three-dimensional (3D) die-stacked processor and (iii) within coherence communication paths of a chip multiprocessor.

We perform a detailed characterization of the loops in a super-scalar pipeline and show that previous attempts to characterize the impact of wire-delays on performance over-estimate the IPC degradation for some loops. We observe that most loops tend to become less critical as more speculation and simple optimizations are introduced. three-dimensional stacking allows dies to be bonded with each other in the vertical dimension enabling further reduction in wire-length. We incorporate the data from the criticality study into a floor-planner that leverages 3D to reduce the lengths of the most critical interblock wires. The overall results argue against leveraging 3D to improve single-core performance and shows that IPC-aware 2D floor-plans perform within an acceptable range of 3D.

Coherence operations on multicore architectures necessitate frequent communication over global on-chip wires. Different coherence messages may have varying delay-tolerance levels. We quantify the sensitivity to wire delays for each type of coherence message in an OoO multiprocessor model employing directory-based cache coherence. We observe that OoO processors are able to hide latency in coherence operations adequately and hence there is potential to save considerable power over the interconnect by employing efficient power-optimization strategies.

# CONTENTS

| AB  | STRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iv                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vii                |

| LIS | ST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | viii               |

| AC  | KNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ix                 |

| CH  | IAPTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                  |

|     | <ul> <li>1.1 Motivation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $2 \\ 5 \\ 5 \\ 6$ |

| 2.  | WIRE DELAYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>7</b>           |

|     | <ul> <li>2.1 Critical Microarchitecture Loops</li> <li>2.1.1 Instruction Fetch Loop</li> <li>2.1.2 Rename Loops</li> <li>2.1.3 Wakeup and Bypass Loops</li> <li>2.1.4 Bypassing Loops Between Groups of Functional Units</li> <li>2.1.5 Cache Hierarchy Loops</li> <li>2.2 IPC Impact of Wire Delays</li> <li>2.2.1 Methodology</li> <li>2.2.2 Behavior of Single Threaded Workloads</li> <li>2.2.3 Comparison with Multithreaded Workloads</li> <li>2.2.4 Dependence of Criticality on Processor Configuration</li> </ul> |                    |

| 3.  | CRITICALITY AWARE FLOORPLANNING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                 |

|     | <ul> <li>3.1 IPC-aware 2D Floorplanning</li> <li>3.2 Optimizing 3D Floorplans</li> <li>3.3 Floorplanning Results</li> <li>3.3.1 Methodology</li> <li>3.3.2 Comparison of Optimal 2D and 3D Floorplans</li> <li>3.3.3 IPC-optimal Floorplanning for In-order</li> <li>and SMT Cores</li> </ul>                                                                                                                                                                                                                              |                    |

|     | 3.3.4 Comparison with Pentium4 Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32                 |

| 4. | COHERENCE MESSAGE CRITICALITY                                                                                                                                                                                                                                                                                                        | 35                                                   |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|    | <ul> <li>4.1 Coherence Message Taxonomy</li> <li>4.2 Motivation</li> <li>4.3 Making Use of Criticality</li> <li>4.3.1 Resource Utilization</li> <li>4.3.2 Power Efficiency</li> <li>4.3.3 Misspeculation Reduction</li> <li>4.4 Coherence Message Analysis</li> <li>4.4.1 Methodology</li> <li>4.4.2 Workload Description</li> </ul> | $35 \\ 37 \\ 38 \\ 38 \\ 39 \\ 40 \\ 40 \\ 40 \\ 40$ |

|    | <ul> <li>4.4.3 Performance Impact of Wire Delays<br/>on Coherence Protocols</li></ul>                                                                                                                                                                                                                                                | 44<br>45<br>48<br>48                                 |

| 5. | RELATED WORK                                                                                                                                                                                                                                                                                                                         | 51                                                   |

| 6. | CONCLUSION AND FUTURE WORK                                                                                                                                                                                                                                                                                                           | 53                                                   |

| AP | PPENDIX: SYNTHETIC BENCHMARK PSEUDOCODE                                                                                                                                                                                                                                                                                              | 55                                                   |

| RE | FERENCES                                                                                                                                                                                                                                                                                                                             | 57                                                   |

# LIST OF FIGURES

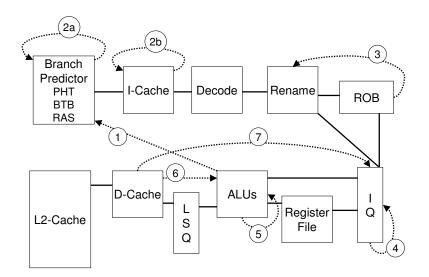

| 2.1 | Critical microarchitectural loops in an O-o-O superscalar pipeline $\ldots$        | 8  |

|-----|------------------------------------------------------------------------------------|----|

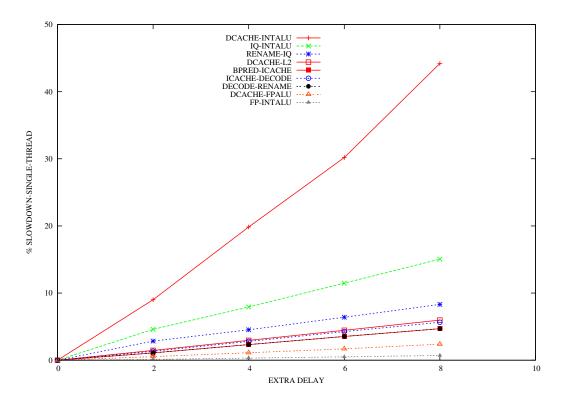

| 2.2 | IPC slowdown curves for single threaded workloads                                  | 15 |

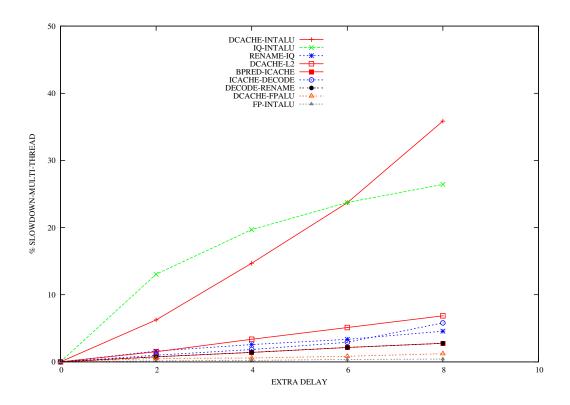

| 2.3 | IPC slowdown curves for multithreaded workloads $\hdots$                           | 16 |

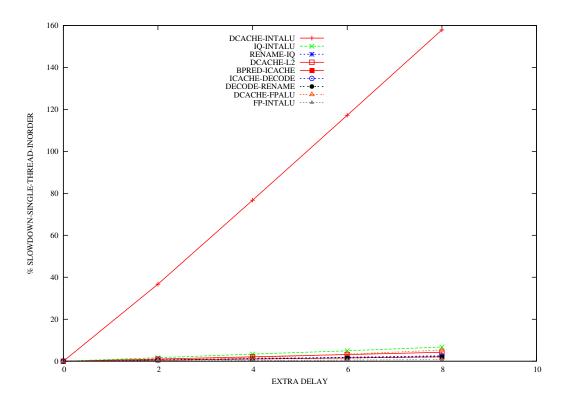

| 2.4 | IPC slowdown curves for an in-order processor configuration                        | 18 |

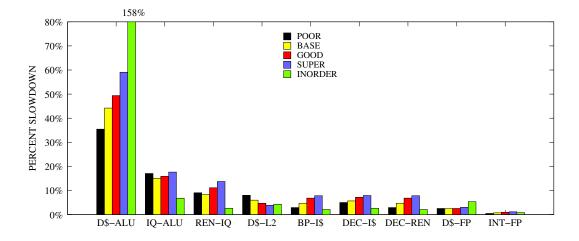

| 2.5 | IPC slowdowns for various processor configurations                                 | 19 |

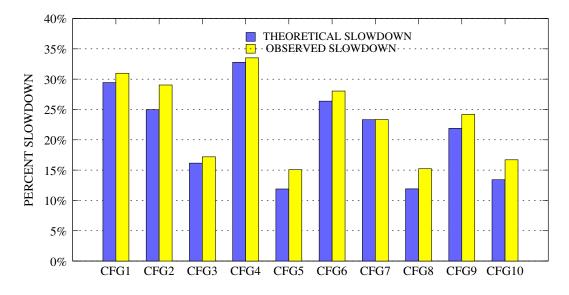

| 3.1 | Additive nature of IPC degradation                                                 | 22 |

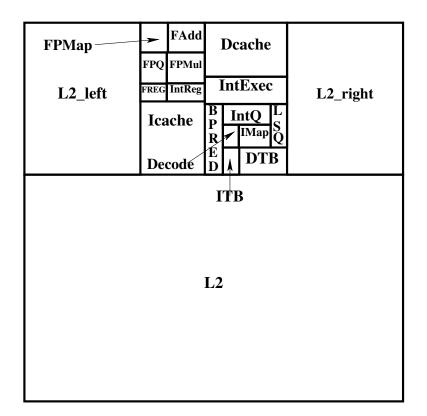

| 3.2 | Optimal 2D floorplan                                                               | 28 |

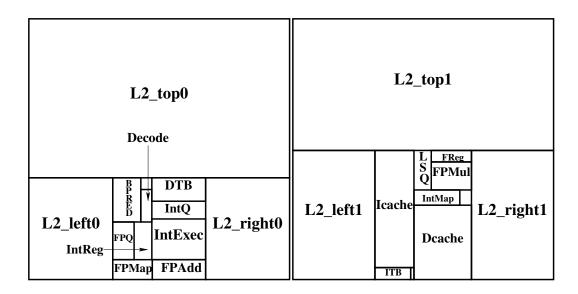

| 3.3 | Optimal 3D floorplan                                                               | 28 |

| 3.4 | Comparison of basic, optimal 2D and optimal 3D floor<br>plans $\ldots\ldots\ldots$ | 29 |

| 3.5 | Normalized CPI of basic and criticality aware floorplans for in-order processors   | 31 |

| 3.6 | Normalized CPI of basic and wire delay aware floorplans for SMT processors         | 32 |

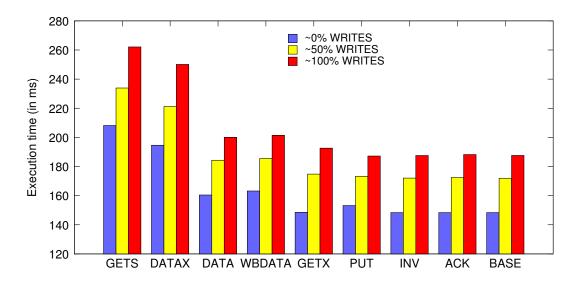

| 4.1 | Execution time impact of wire delay on the synthetic benchmark $\ldots$ .          | 44 |

| 4.2 | Variation with different write-set sizes                                           | 46 |

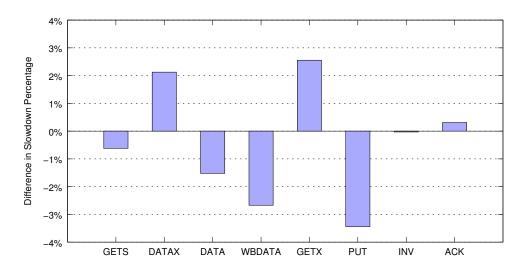

| 4.3 | Difference in slowdown between $0\%$ and $100\%$ write-set size                    | 46 |

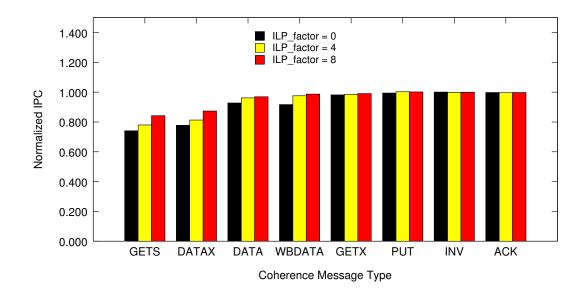

| 4.4 | Performance impact under different levels of available ILP $\ldots$                | 47 |

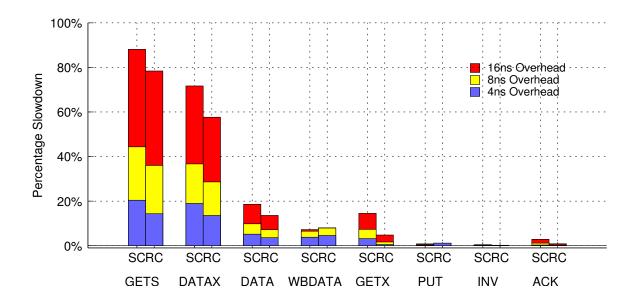

| 4.5 | Slowdown percentage for sequential and relaxed consistency models                  | 49 |

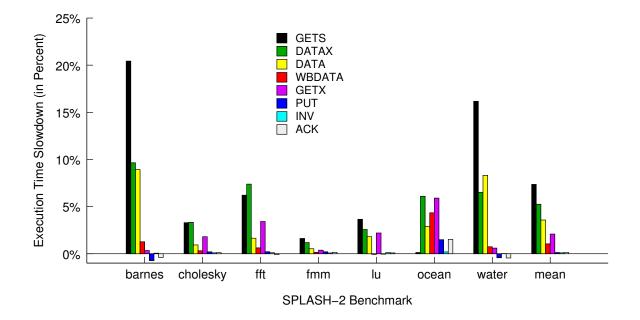

| 4.6 | Percentage slowdown for SPLASH-2 benchmarks                                        | 49 |

# LIST OF TABLES

| 2.1 | Effect of wire delays on critical loops                                                                                           | 13 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | SimpleScalar simulator parameters                                                                                                 | 14 |

| 2.3 | Benchmark pairs for the multithreaded workload                                                                                    | 14 |

| 2.4 | Parameters for five different processor configurations                                                                            | 19 |

| 3.1 | Critical path latencies for 10 random configurations                                                                              | 22 |

| 3.2 | 3D floorplanner cost function parameters                                                                                          | 24 |

| 3.3 | Weights for the different pairs of blocks and the corresponding wire delays for the least constrained and most constrained models | 26 |

| 3.4 | Thermal model parameters                                                                                                          | 27 |

| 3.5 | Optimal floor<br>plan temperatures in $^{\circ}\mathrm{C}$                                                                        | 30 |

| 4.1 | Coherence message groupings                                                                                                       | 41 |

| 4.2 | Opal parameters                                                                                                                   | 42 |

| 4.3 | Ruby parameters                                                                                                                   | 42 |

| 4.4 | Synthetic benchmark input parameters                                                                                              | 43 |

| 4.5 | Breakdown of instructions and memory operations per $CPU \dots \dots$                                                             | 43 |

| 4.6 | Bandwidth consumption of different message types                                                                                  | 45 |

## ACKNOWLEDGEMENTS

I am grateful to my advisor Prof. Rajeev Balasubramonian for being my mentor and inspiration throughout my graduate school life. All credit for opening me up to the world of computer architecture, a place where I never thought I would be, falls squarely on his shoulders. I thank my committee members Prof. John Carter and Prof. Ganesh Gopalakrishnan for their valuable guidance and comments on my work. I thank Abhishek Ranjan, Manu Awasthi and Devyani Ghosh for their collaboration in parts of this work. I also thank Niti Madan and Liqun Cheng for their valuable help with the SMT Model for SimpleScalar and the Wisconsin GEMS memory model respectively. I thank all fellow Impulse lab mates and architecture reading club members for making my years in graduate school thoroughly enjoyable. Finally I would like to thank my parents, brother and friends for their unconditional love and support through all my endeavours.

# CHAPTER 1

# INTRODUCTION

Advancements in silicon fabrication technology have driven improvements in processor performance because of smaller transistor sizes. The reasons for improvement are twofold: smaller sizes allow greater transistor densities and hence more complex functionality, and secondly the logic delay of a transistor also reduces because of smaller gate lengths. However, with smaller transistor sizes, wire width and height also decrease, resulting in larger wire resistances. The increased resistance coupled with faster clock rates and increasing die area will cause wire delay between micro-architectural blocks to extend beyond tens of cycles. Hence wire delay is becoming a critical component of overall performance, limiting the effectiveness of architectural features that require global communication or unduly increasing the distance between portions of a processor. This work illustrates the importance of studying the impact of these wire delays on the overall performance of a processor.

In recent years, power density and chip temperature have emerged as primary constraints in microprocessor design. They become more critical with every new process generation because of increased transistor and power densities. The move to a 3D die stacked chip [1, 2, 3] further accelerates the climb on the power density curve. An effective technique to overcome the temperature bottleneck is micro-architectural floorplanning. By placing relatively cool blocks around hot blocks, the rate of lateral heat spreading is improved, thereby reducing the operating temperature of hotspots. Floorplanning algorithms typically employ a simulated annealing process where a large number of arbitrary arrangements of blocks (such as the register file, rename unit, branch predictor, etc.) are evaluated based on an objective function. The objective function attempts to find a floorplan that minimizes temperature, metal or silicon area and wire density with little regard to the performance impact of varying interblock wirelengths.

#### 1.1 Motivation

To date, no architectural study has provided a detailed characterization of how wire delays between micro-architectural blocks impact performance. Most papers on floorplanning [4, 5, 6] employ performance models that are not very detailed or even have some flaws. For example, these studies [5, 6] indicate that certain wire delays can degrade performance by as much as 65%, but do not consider simple pipeline optimizations that can dramatically cut down these effects. We present results that can serve as an authoritative guideline that VLSI researchers can directly adopt in their floorplanning or routing/placement tools.

The performance data from this work can also be useful in another important context. The vertical stacking of dies allows microprocessor circuits to be implemented across three dimensions. This allows a reduction in distances that signals must travel. By reducing overall wire lengths, 3D implementations can help alleviate the performance and power overheads of on-chip wiring. The primary disadvantage of 3D chips is that they cause an increase in power densities and on-chip temperatures. The true potential of 3D can be estimated only with knowledge of the criticality of different interblock wires.

Many recent advances have been made in fabricating 3D chips ([7] presents a good overview). This technology can incur a nontrivial cost because of increased design effort, reduced manufacturing yield, and higher cooling capacities. Even though the technology is not yet mature, early stage architecture results are required to understand its potential. There are likely three primary avenues where 3D can provide benefits:

• 3D stacking of DRAM chips upon large scale Chip Multi Processors (CMP): Interdie vias can take advantage of the entire die surface area to implement a high bandwidth link to DRAM, thereby addressing a key bottleneck in CMPs that incorporate over hundred cores [8, 2].

- "Snap-on" analysis engines: Chips employed by application developers can be fitted with additional stacked dies that contain units to monitor hardware activity and aid in debugging [9]. Chips employed by application users will not incorporate such functionality, thereby lowering the cost for these systems.

- Improvement in CPU performance/power: The components of a CPU (cores, cache banks, pipeline stages, individual circuits) can be implemented across multiple dies. By lowering the penalties imposed by long wires, performance and power improvements are possible.

The third approach above can itself be classified in two ways: *folding* partitions a single structure (e.g., register file) across multiple dies in order to reduce its access time; *stacking* preserves the structure of individual circuit blocks but leverages 3D to reduce interblock distances. Most recent work has focused on the *folding* approach [10, 11, 12, 13, 14, 15]. Results have shown that this can typically help reduce the delays within a pipeline stage by about 10%, which in turn can contribute to either clock speed improvements or ILP improvements (by supporting larger structures at a target cycle time). The disadvantage with the folding approach is that potential hotspots (e.g., the register file) are partitioned and placed vertically, further exacerbating the temperature problem. Much design effort will also be invested in translating well established 2D circuits into 3D.

The primary advantage of the *stacking* approach is the ability to reduce operating temperature by surrounding hotspots with relatively cool structures. It also entails less design complexity as traditional 2D circuits can be re-used. A third advantage is a reduction in wire delay/power for interconnects between various micro-architectural structures. It has, however, received relatively little attention. We intend to focus on this approach by integrating many varied aspects (loop analysis, pipeline optimizations, SMT, automated floorplanning) in determining the impact of 3D on single core performance. To understand the potential benefit of the stacking approach, however, it is necessary that we first quantify the performance impact of wire delays between micro-architectural structures.

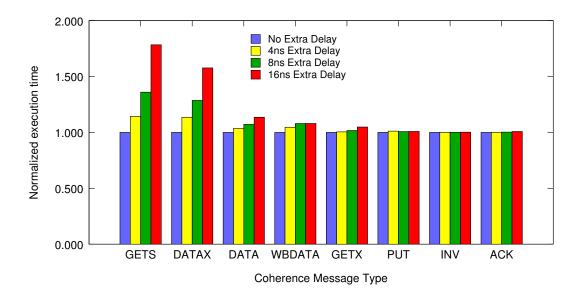

A study of wire delays can also be useful when applied to coherence protocols. In future microprocessors, as the number of cores scales beyond tens and hundreds, more scalable coherence protocols are needed, and directory based designs have been most popular so far [16, 17]. Several studies [18, 19, 20, 21, 22] have characterized the high frequency of cache misses in parallel workloads, and how these misses significantly hurt the total execution time. On a cache miss, a variety of protocol actions are initiated, such as request messages, invalidation messages, intervention messages, data block write backs, data block transfers, etc. Every coherence message involves on-chip communication with latencies that are projected to grow to tens of cycles in future billion transistor architectures [23]. Some of these can tolerate long latencies, whereas others are on the program critical path. Further, speculation within the core can hide the cost of some of these wire delays. For example, on a cache write miss, the requesting processor may have to wait for data from the home node (a two hop transaction), and for acknowledgments from other sharers of the block (a three hop transaction). Since acknowledgments are on critical path, every cycle of delay in acknowledgments has higher chances to hurt performance than a data block transfer delayed by a cycle. However, an in-depth analysis of the delay sensitivities of coherence messages is required to comprehend the bigger picture.

Cheng et al. [24, 25] have shown that different coherence protocol messages in a directory based protocol have varying bandwidth and latency needs. This is done by identifying message flows within the context of individual coherence operations. However, such an analysis is incognizant of the frequency of the different coherence operations and the interactions among them. For example, the study reports invalidate messages as being critical to performance. However, that may not always be the case; invalidates may not be so frequent as to make a difference in overall performance. A more detailed analysis of the delay sensitivities of coherence messages for an application as a whole will be more beneficial. Our analysis considers the effect of wire delays in directory based coherence protocols for out-of-order execution engines.

### **1.2** Thesis Statement

We believe that the criticality analysis of wire delays in the context of uniprocessors or shared memory multiprocessors will prove as an effective tool to selectively optimize a system for performance or power. This thesis corroborates this statement by applying such an analysis in two contexts, for micro-architectural loops within a pipeline and for coherence communication paths in a shared memory multiprocessor system.

The thesis incorporates the results of the loop analysis into a floorplanning algorithm to produce performance optimized floorplans. The criticality data are also used to identify the effectiveness of the 3D *stacking* approach. The data from the wire delay study within coherence protocols will be used to isolate coherence messages that can be optimized for latency and for power. Other intuitive techniques, not within the scope of this thesis, to utilize the criticality information are discussed.

### **1.3** Contributions

In this thesis, we expose the impact of wire delays on processor performance and highlight the significance of criticality awareness on processor designs. The primary contributions of this thesis are:

- Carries out the most comprehensive analysis of the impact of wire delays on critical micro-architectural loops of a traditional out-of-order processor pipeline that takes into consideration several common pipeline optimizations. The analysis also identifies and addresses areas where past work is inaccurate.

- Designs and implements a criticality aware floorplanner based on input from the wire delay study. The detailed models of the wire delay analysis help in accurately characterizing the IPC penalty of each critical loop. Our floorplan-

ners are able to automate the process of identifying layouts that minimize the lengths of these critical wires.

- Extends the methodology stated above to generate wire delay optimal 3D floorplans that utilize the extra dimension to minimize critical wire lengths between different units. This enables researchers to draw a conclusion about the effectiveness of the 3D stacking approach.

- Identifies the delay tolerance levels exhibited by coherence messages in a shared memory multiprocessor environment where coherence is maintained with the help of a directory based protocol. We explore variations in sensitivity to wire delay for different consistency models. We propose a list of hardware techniques that incorporate criticality awareness in coherence protocols for improved performance or power efficiency.

### 1.4 Outline

Before we begin with the criticality analysis of micro-architectural loops, it is essential to identify the factors affecting performance for each of these loops. Chapter 2 qualitatively describes the relationships between wire delays and critical micro-architectural loops, and quantifies these relationships for single and multithreaded superscalar cores. In Chapter 3, these data are then fed into floorplanning algorithms to derive layouts for 2D and 3D chips that optimize a combination of metrics. We show that 2D layouts are able to minimize the impact of critical wire delays effectively. This result is more optimistic about 2D layouts than some prior work in the area and there is little room for improvement with a 3D implementation for traditional simple superscalar cores. The motivation for performing a criticality analysis on coherence protocols and a few possible techniques to utilize the information are discussed in Chapter 4. We also present the methodology for our evaluation and detail the results of the coherence message analysis. We discuss related work in Chapter 5 and summarize our conclusions and possible future work in Chapter 6.

## CHAPTER 2

## WIRE DELAYS

An out-of-order superscalar processor has a number of communication paths between microarchitectural structures. For a large enough processor operating at a high frequency, some of these paths may incur multicycle delays. For example, the Pentium4 has a few pipeline stages dedicated for wire delay [26]. A state-of-the-art floorplanning algorithm must attempt to place microarchitectural blocks in a manner that minimizes delays for interblock communication paths, but even the best algorithms cannot completely avoid these delays. As examples, consider the following wire delays that are encountered between pipeline stages in the Pentium4. The floating point, integer, and load/store units cannot all be colocated: this causes the load-to-use latency for floating point operands to be higher than that for integer operands. A recent paper by Black et al. [27] indicates that multicycle wire delays are encountered between the extreme ends of the L1 data cache and integer execution units. Similarly, the paper mentions that wire delays are introduced between the FP register file and FP execution units because the SIMD unit is placed closest to the FP register file (SIMD access to the register file is considered more critical). By introducing a third dimension, we can help reduce on-chip distances and the overall performance penalty of interblock wire delays.

To understand this benefit of 3D, we must first quantify the impact of interblock wire delays on performance and evaluate if 2D floorplanning algorithms yield processors that incur significant IPC penalties from wire delays. In addition to serving as the foundation for our 3D layout study, the data produced here can serve as useful inputs for groups researching state-of-the-art floorplanning tools. It should be noted that while similar analyses exist in the literature, a few papers report inaccurate results because of simplified models for the pipeline.

### 2.1 Critical Microarchitecture Loops

Consider the superscalar out-of-order pipeline shown in Figure 2.1. The pipeline is decomposed into the standard microarchitectural blocks and key data transfers between blocks are indicated with solid lines. Borch et al. [28] define a microarchitectural loop as the communication of a pipeline stage's result to the input of that same pipeline stage or an earlier stage. Loops typically indicate control, data, or structural dependences. The length of the loop is the number of pipeline stages between the destination and origin of the feedback signal. If the length of the loop is increased, it takes longer to resolve the corresponding dependence, thereby increasing the gap between dependent instructions and lowering performance. If a floorplanning tool places two microarchitectural structures far apart and introduces wire delays between them (in the form of additional pipeline stages for signal transmission), the lengths of multiple loops may be increased. Hence, to understand the IPC impact of wire delays, we must understand how the length of a loop impacts IPC. Similar, but less detailed evaluations have also been carried out in prior work (such as [28, 29, 6, 30]). The dashed lines in Figure 2.1 represent important loops

Figure 2.1. Critical microarchitectural loops in an O-o-O superscalar pipeline

within an out-of-order superscalar processor and each loop is discussed next.

#### 2.1.1 Instruction Fetch Loop

In a simple pipeline, the process of instruction fetch involves the following steps: the PC indexes into the branch predictor system to produce the next-PC, the corresponding line is fetched from the Instruction cache (I-cache), instructions are decoded, and when the next control instruction is encountered, it is fed back to the branch predictor system. This represents a rather large loop with a few stall cycles in fetch every time a control instruction is encountered. Introducing wire delays between the branch predictor, I-cache, and decode can severely degrade performance and this pessimistic model was assumed in HotFloorplan [6]. However, it is fairly straightforward to decouple the branch predictor and I-cache so that we instead have two short loops (labeled 2a and 2b in Figure 2.1). Such decoupled pipelines have been proposed by academic [31] and industrial groups [32].

In one possible implementation, the output of the branch predictor (the start of the next basic block) is fed as input back to the branch predictor. As a result, the branch predictor system is now indexed with the PC that starts the basic block, not the PC that terminates the basic block. Updates to the branch predictor system must correspondingly also use the basic block start PC. This allows the branch predictor to produce basic block start PCs independent of the rest of the front end. Our results show that this change in the branch predictor algorithm has a minimal impact on its accuracy. The outputs of the branch predictor can be buffered at the I-cache. Every cycle, the I-cache reads out either the line corresponding to the next queued basic block or the next sequential line if a control instruction is not encountered. Since the presence of a control instruction in the fetched line is not known until the end of decode, a bit is maintained for every I-cache line to indicate if the line contains a control instruction. This bit is set after the line is decoded the first time. Thus, the I-cache can produce a new line every cycle. I-cache fetch cycles are wasted only if the line is being decoded the first time and the default prediction is incorrect.

The front end pipeline now consists of two major tight loops: the branch

predictor loop (2a) and the I-cache loop (2b). The front end is also part of the branch mispredict resolution loop (1), which feeds from the ALU stage all the way back to the front end. Thus, the primary impact of introducing a wire delay between front end pipeline stages is an increase in branch mispredict penalty. Our relative results will hold true even if a different front end pipeline implementation (such as the next-line-and-set predictor in the Alpha 21264 I-cache [32]) is adopted, as long as the critical loops are short. Prior studies [5, 33, 6] have overstated the IPC impact of this wire delay because the branch predictor and I-cache were assumed to not be decoupled.

#### 2.1.2 Rename Loops

The introduction of wire delays either between the decode and rename stages or between the rename and issue queue stages lengthens the penalty for a branch mispredict (loop 1). Since registers are allocated during rename, wire delays between the rename stage and the issue queue increase the duration that a register entry remains allocated (loop 3). This increases the pressure on the register file and leads to smaller in-flight instruction windows.

#### 2.1.3 Wakeup and Bypass Loops

There is a common misconception that wire delays between the issue queue and ALUs lead to stall cycles between dependent instructions [5, 6]. This is not true because the pipeline can be easily decomposed into two tight loops: one for wakeup (loop 4) and one for bypass (loop 5). When an instruction is selected for issue in cycle N, it first fetches operands from the register file, potentially traverses long wires, and then reaches the ALU. Because of these delays, the instruction may not begin execution at the ALU until the start of cycle N + D. If the ALU operation takes a single cycle, the result is bypassed to the inputs of the ALU so that a dependent instruction can execute on that ALU as early as the start of cycle N+D+1. For this to happen, the dependent instruction must leave the issue queue in cycle N + 1. Therefore, as soon as the first instruction leaves the issue queue, its output register tag is broadcast to the issue queue so that dependents can leave the issue queue in the next cycle. Thus, operations within the issue queue must only be aware of the ALU latency, and not the time it takes for the instruction to reach the ALU (delay D). The gap between dependent instructions is therefore not determined by delay D, but by the time taken for the wakeup loop and by the time taken for the bypass loop (both of these loops were assumed to be 1 cycle in the above example). The introduction of wire delays between the issue queue and ALU because of floorplanning will not impact either of these loops.

However, wire delays between the issue queue and ALU will impact another critical loop that (has been disregarded by every floorplanning tool to date. This is the load hit speculation loop (loop 7 in Figure 2.1). The issue queue schedules dependent instructions based on the expected latency of the producing instruction. While most instructions have fixed latencies, a load instruction's latency depends on the location of data in the cache hierarchy. In modern processors, such as the Pentium4 [26], the issue queue optimistically assumes that the load will hit in the L1 data cache and accordingly schedules dependents. If the load latency is any more than this minimum latency, dependent instructions that have already left the issue queue are squashed and subsequently replayed. To facilitate this replay, instructions can be kept in the issue queue until the load latency is known. Thus, load-hit speculation negatively impacts performance in two ways: (i) replayed instructions contend twice for resources, (ii) issue queue occupancy increases, thereby supporting a smaller instruction window, on average. The first factor comes into play on a load-hit misspeculation, whereas the second factor impacts performance even for correct speculations.

If any wire delays are introduced in the pipeline between the issue queue and ALU, or between the ALU and data cache, it takes longer to determine if a load is a hit or a miss. Correspondingly, the penalties for correct and incorrect load-hit speculations increase. We also model the Tornado effect [34], where an entire chain of instructions dependent on the load are issued, squashed, and replayed on a load miss. Delays between the issue queue and ALUs also impact branch mispredict penalty and register occupancy. They also increase the L1 miss penalty as it takes

longer to restart the pipeline after an L1 miss.

#### 2.1.4 Bypassing Loops Between Groups of Functional Units

For this discussion, we assume that the functional units are organized as three clusters: integer ALUs, floating-point ALUs, and memory unit. The memory unit is composed of the load-store queue (LSQ) and L1 data cache. The ALUs that compute the effective addresses for loads and stores are part of the integer cluster. Bypassing within a cluster does not cost additional cycles. If wire delays are introduced between the integer and floating-point clusters, performance will be impacted for those integer operations that are data dependent on a floating-point result, and vice versa. The introduction of wire delays between the integer cluster and memory unit impacts the load-to-use latency (loop 6 in Figure 2.1) and the penalties for load-hit speculation.

If a single cycle delay is introduced between the memory and integer units, the load-to-use latency increases by two cycles. Similarly, wire delays between levels of the cache hierarchy will increase the cache miss penalties. If a single cycle delay is introduced, it takes one more cycle to communicate the effective address to the cache and an additional cycle to forward the value back to dependent instructions in the integer cluster. Even if the ALU that generates the effective address is part of the memory unit, the penalty is similar because a register value produced in the integer cluster will likely have to be forwarded as input to the ALU. As a result, the gap between a load and a dependent integer operation increases by two cycles. Similarly, if a single cycle wire delay is introduced between the memory unit and floating-point cluster, the gap between a load and a dependent floating-point operation increases by one cycle.

Now consider the case where the integer ALUs are themselves distributed across multiple clusters, similar to the Alpha 21264 [32] micro-architecture. Bypassing an operand within a cluster imposes little wire delay penalty, but bypassing an operand between clusters is more expensive. An instruction steering heuristic attempts to balance load across clusters and steer dependent instructions to the same cluster. However, it is impossible to localize all dependent instructions and typically, there exist numerous critical intercluster data transfers. An increase in intercluster wire delays will therefore increase the gap between every pair of dependent instructions that are assigned to different clusters.

#### 2.1.5 Cache Hierarchy Loops

The wire delay between the L1 data cache controller and the L2 cache controller directly impacts the latency for an L1 data cache miss. Similarly, the delay between the L1 instruction cache controller and the L2 cache controller impacts the latency for an L1 instruction cache miss. Table 2.1 summarizes the different ways that wire delays can impact performance.

# 2.2 IPC Impact of Wire Delays

#### 2.2.1 Methodology

The simulator used in this study is based on SimpleScalar-3.0 [35], a cycleaccurate simulator for the Alpha AXP architecture. It is extended to not only model multiple threads and separate issue queues, register files, and reorder buffer, but also the microarchitectural loops and features discussed in Section 2.1. For each of the critical sets of pipeline stages listed in Table 2.1, we introduce additional wire delays of 2, 4, 6, and 8 cycles. The single thread benchmark suite includes 23 SPEC-2k programs, executed for 100 million instruction windows identified by the Simpoint tool [36]. Table 2.2 lists the processor parameters for the base configuration.

| Pipeline stages                | Critical loops affected                           |  |  |

|--------------------------------|---------------------------------------------------|--|--|

| Branch predictor and L1I-Cache | Branch mispredict penalty                         |  |  |

| I-Cache and Decode             | Branch mispredict penalty, penalty to detect con- |  |  |

|                                | trol instruction                                  |  |  |

| Decode and Rename              | Branch mispredict penalty                         |  |  |

| Rename and Issue queue         | Branch mispredict penalty and register occupancy  |  |  |

| Issue queue and ALUs           | Branch mispredict penalty, register occupancy,    |  |  |

|                                | L1 miss penalty, load-hit speculation penalty     |  |  |

| Integer ALU and L1D-Cache      | Load-to-use latency, L1 miss penalty, load-hit    |  |  |

|                                | speculation penalty                               |  |  |

| FP ALU and L1D-Cache           | Load-to-use latency for floating-point operations |  |  |

| Integer ALU and FP ALU         | Dependences between integer and FP operations     |  |  |

| L1 caches and L2 cache         | L1 miss penalty                                   |  |  |

Table 2.1. Effect of wire delays on critical loops

| ц | able 2.2. SimpleScalar simulator parameters |                    |                    |                                |  |  |  |  |  |  |

|---|---------------------------------------------|--------------------|--------------------|--------------------------------|--|--|--|--|--|--|

|   | Fetch queue size                            | 16                 | Branch predictor   | comb. of bimodal and 2-level   |  |  |  |  |  |  |

|   | Bimodal predictor size                      | 16K                | Level 1 predictor  | 16K entries, history 12        |  |  |  |  |  |  |

|   | Level 2 predictor                           | 16K entries        | BTB size           | 16K sets, 2-way                |  |  |  |  |  |  |

|   | Branch mispredict penalty                   | at least 10 cycles | Fetch width        | 4                              |  |  |  |  |  |  |

|   | Dispatch width                              | 4                  | Commit width       | 4                              |  |  |  |  |  |  |

|   | Issue queue size                            | 20 Int, 20 FP      | Register file size | 80 (Int and FP, each)          |  |  |  |  |  |  |

|   | Integer ALUs/mult-div                       | 4/2                | FP ALUs/mult-div   | 2/1                            |  |  |  |  |  |  |

|   | L1 I-cache                                  | 32KB 2-way         | Memory latency     | 300 cycles for the first block |  |  |  |  |  |  |

|   | L1 D-cache                                  | 32KB 2-way 2-cycle | L2 unified cache   | 2MB 8-way, 30 cycles           |  |  |  |  |  |  |

|   | ROB/LSQ size                                | 80/40              | I and D TLB        | 128 entries, 8KB page size     |  |  |  |  |  |  |

Table 2.2.

SimpleScalar simulator parameters

We also repeat our experiments for a core that supports the execution of two threads in SMT fashion and a traditional in-order core. For the multithreaded workload, we form a benchmark set that consists of 10 different pairs of programs. Programs are paired to generate a good mix of high IPC, low IPC, FP, and Integer workloads. Table 2.3 shows our benchmark pairs. Each of the multithreaded workloads are executed until the first thread commits 100 million instructions. Our SMT model employs the ICOUNT [37] fetch policy and all resources (except the ROB) are dynamically shared by the two threads.

#### 2.2.2 Behavior of Single Threaded Workloads

The resulting IPC degradation curves (averaged across the benchmark suite), relative to the baseline processor (that imposes zero interblock wire delay penalties), are charted in Figure 2.2 for single threaded workloads. For the single threaded workloads, it is evident that wire delays between the ALU and data cache have the greatest impact on performance, causing an average slowdown of 20% for a four cycle delay. Integer programs are impacted more than FP programs, with some benchmarks exhibiting slowdowns of greater than 40%. As shown in Table 2.1, delays between the ALU and data cache affect multiple critical loops. The load-to-

| <br>abio 100. Benefiliarii paris for the materineaded wormoad |       |                   |               |       |                  |  |  |  |  |

|---------------------------------------------------------------|-------|-------------------|---------------|-------|------------------|--|--|--|--|

| Benchmark Set                                                 | Set # | IPC Pairing       | Benchmark Set | Set # | IPC Pairing      |  |  |  |  |

| swim-applu                                                    | 1     | FP/FP/Low/High    | bzip-fma3d    | 2     | Int/FP/Low/High  |  |  |  |  |

| bzip-vortex                                                   | 3     | Int/Int/Low/Low   | eon-art       | 4     | Int/FP/High/Low  |  |  |  |  |

| eon-vpr                                                       | 5     | Int/Int/High/High | gzip-mgrid    | 6     | Int/FP/Low/Low   |  |  |  |  |

| mesa-equake                                                   | 7     | FP/FP/High/High   | swim-lucas    | 8     | FP/FP/Low/Low    |  |  |  |  |

| twolf-equake                                                  | 9     | Int/FP/High/High  | vpr-gzip      | 10    | Int/Int/High/Low |  |  |  |  |

Table 2.3. Benchmark pairs for the multithreaded workload

Figure 2.2. IPC slowdown curves for single threaded workloads

use loop contributes nearly three-fourth of the 20% observed slowdown, with the remaining attributed to the load-hit speculation loop (1.7%), and L1 miss penalty loop (2.6%).

The load-hit speculation loop also contributes to the second most critical wire delay, that between the issue queue and ALUs. Since the wakeup and bypass loops are decoupled, a four cycle wire delay between the issue queue and ALU only causes a performance degradation of 8%, much lower than the pessimistic 65% degradation reported in [6]. Similarly, because of the decoupled front end, a four cycle wire delay between the branch predictor and I-cache only causes a 2.3% performance loss (instead of the 50% performance loss reported in [6]).

To establish confidence in our simulation infrastructure, we modeled the coupled IQ-ALU and front-end in an attempt to reproduce the results in [48]: we observed slowdowns of 68% and 41%, respectively, quite similar to the numbers reported in [48]. The new branch predictor algorithm (indexing with basic block start address

instead of basic block end address) affects accuracy by 0.55%. Only 1.14% of all fetched branches introduce stalls in fetch because the line is new in the I-cache and the bit indicating the presence of a control instruction is not set. All other wire delays are noncritical and cause slowdowns of less than 5% (for a four cycle delay).

#### 2.2.3 Comparison with Multithreaded Workloads

Figure 2.3 shows results for multithreaded workloads. Since the multithreaded workloads only include a subset of all programs, we normalize the multithread slowdowns against the single thread slowdowns observed for those programs. Hence, it is a reasonable approximation to directly compare the data in the two graphs of Figure 2.2 and Figure 2.3. For almost all loops, the multithreaded processor is slightly less sensitive to wire delays because it can find useful work in other threads during stall cycles. The only exception is the IQ-ALU loop. Wire delays in the IQ-ALU loop increase the load-hit speculation penalty. An increase in this delay causes the thread to issue more speculative instructions: hence wire delays are an

Figure 2.3. IPC slowdown curves for multithreaded workloads

impediment to the execution of the co-scheduled thread, not an opportunity to steal idle slots. Further, as this wire delay increases, issue queue occupancy increases and since this is a shared resource, it further inhibits the co-scheduled thread.

There are two reasons that could be attributed to this phenomenon. (i) The IQ-ALU loop is slightly different from the other loops. An increase in other delays causes a thread to sit idle allowing another thread to fill in the slack. For loadhit-speculation, increasing the loop length causes the thread to continue issueing dependents, so regardless of the presence of another thread, some penalty is being imposed. (ii) The IQ-ALU loop increases the Issue queue occupancy, which in turn could inhibit instructions from other threads from being issued.

#### 2.2.4 Dependence of Criticality on Processor Configuration

Next, we examine various processor design points to verify if the criticality of wire delays is a function of the processor model and configuration.

We first consider a processor with strict in-order execution and also plot its slowdown. Figure 2.4 shows the corresponding curves. The parameters of the simulated processor are similar to the base out-of-order parameters of Table 2.2. We observe that the DCACHE-ALU loop stands out as the only critical loop with an average slowdown of 77% for all benchmarks for an eight cycle delay. Wire delay between the DCACHE and the ALUs adversely affects performance because not only do they affect instructions in the load's dependence chain, as in the case of the out-of-order pipeline, but they could possibly stall all instructions following the first consumer as they wait for it to proceed to the next pipe stage. Also, the ALU to IQ loop is not as critical relative to the out-of-order processor configuration. It experiences a slowdown of only 3.4% compared to 8% slowdown in performance for the OoO core. This is because, at any point in time the number of uncommitted in-flight instructions in the window is few compared to an out-of-order model. Hence, there is little pressure on the register file and causes no stalls related to register unavailability. All other loops experience an insignificant slowdown due to wire delays.

The properties for four out-of-order processors (ranging from "Poor" to "Su-

Figure 2.4. IPC slowdown curves for an in-order processor configuration

per") and the in-order configuration are summarized in Table 2.4. Figure 2.5 demonstrates the IPC degradation when eight cycles of wire delay are introduced between each set of pipeline stages for all five processor configurations. For all the out-of-order configurations, our broad conclusions hold true: the ALU-Dcache delay is most critical, followed by the IQ-ALU delay. However, we can see that the magnitude of the slowdown due to the ALU-Dcache delay increases as we go from a poor configuration to a good configuration. The rationale behind this is that in a high-IPC model, any available ILP is quickly mined. Long latency operations tend to be on the critical path and any additional delays to these instructions will almost certainly increase overall execution time. And as we saw, for the in-order model the ALU-Dcache delay stands out, yielding a 157% performance slowdown. Note that a single cycle wire delay between the ALU and Dcache increases load latency by two cycles, effectively stalling all subsequent instructions in the in-order processor by two additional cycles.

|                    | Poor            | Base  | Good  | Super | Inorder  |

|--------------------|-----------------|-------|-------|-------|----------|

| Issue              | 0-0-0           | 0-0-0 | 0-0-0 | 0-0-0 | in-order |

| Dec/Iss/Comm width | 4               | 4     | 8     | 8     | 4        |

| ROB size           | 56              | 80    | 128   | 256   | 80       |

| L1-Dcache          | 16K             | 32K   | 64K   | 128K  | 32K      |

| L1-Icache          | 16K             | 32K   | 64K   | 128K  | 32K      |

| L2-cache           | $1 \mathrm{MB}$ | 2MB   | 4MB   | 4MB   | 2MB      |

| Mem. Ports         | 2               | 2     | 2     | 4     | 2        |

| IntALU/IntMul      | 2/1             | 4/2   | 6/2   | 8/4   | 4/2      |

| FPALU/FPMul        | 2/1             | 2/1   | 4/1   | 8/2   | 2/1      |

Table 2.4. Parameters for five different processor configurations

Figure 2.5. IPC slowdowns for various processor configurations

For our study in Chapter 3 and results in Section 3.3, we assume single threaded workloads and only consider the single threaded slow-down curves of Figure 2.2. However, a sensitivity analysis of our floorplanning algorithms to in-order and multithreaded workloads is presented in Section 3.3.3

# CHAPTER 3

# CRITICALITY AWARE FLOORPLANNING

A chip's operating temperature is emerging as a major design constraint. Floorplanning is an effective technique that helps spread heat and minimize the occurrence of localized hotspots. The floorplanning process may place two communicating microarchitectural blocks (for example, the issue queue and ALU) far apart in an attempt to surround hot blocks with relatively cooler blocks. As we move to future wire bound technologies, multiple pipeline stages may be required for the communication of signals between blocks that are placed far apart. An intelligent floorplanning algorithm should also strive to place blocks communicating over a critical path close to each other. The slowdown curves in Chapter 2 are indicative of the criticality of each interblock wire. In this section, we will discuss how a floorplanning algorithm can efficiently incorporate this data to produce floorplans tuned for performance.

## 3.1 IPC-aware 2D Floorplanning

Floorplanning algorithms [29, 38, 39, 6] typically employ a simulated annealing process to evaluate a wide range of candidate floorplans. The objective functions for these algorithms attempt to minimize some combination of silicon/metal area, wire power, and chip temperature. In modern microprocessors, since delays across global wires can exceed a single cycle, a floorplanning tool must also consider the performance impact of introducing multicycle wire delays between two communicating microarchitectural blocks. The objective function in a state-of-the-art floorplanner can be represented as follows [29, 38, 39, 6]:

$\lambda_A \times Area\_metric + \lambda_T \times Temperature$

+

$$\sum_{ij} \lambda_W \times W_{ij} \times Activity_{ij}$$

+  $\sum_{ij} \lambda_I \times d_{ij} \times IPC\_penalty_{ij}$

In the equation above,  $\lambda_A$ ,  $\lambda_T$ ,  $\lambda_W$ , and  $\lambda_I$  represent constants that tune the relative importance of each metric (area, temperature, wire power, and IPC),  $W_{ij}$  represents the metal area (length × number of wires) between microarchitectural blocks *i* and *j*, Activity<sub>ij</sub> captures the switching activity for the wires between blocks *i* and *j*, the metric  $d_{ij}$  represents the distance between blocks *i* and *j* in terms of cycles, while  $IPC\_penalty_{ij}$  is the performance penalty when a single cycle delay is introduced between blocks *i* and *j*. The metrics  $W_{ij}$ ,  $d_{ij}$ , Temperature, and Area\\_metric are computed for every floorplan being considered, while metrics Activity<sub>ij</sub> and  $IPC\_penalty_{ij}$  are computed once with an architectural simulator and fed as inputs to the floorplanner. The design of efficient floorplanners remains an open problem and many variations to the above objective function can be found in the literature.

When a floorplanning algorithm evaluates a floorplan with various wire delays between pipeline stages, it must predict the expected overall IPC. If the effects of different wire delays are roughly additive, it is fairly straightforward to predict the IPC of a configuration with arbitrary wire delays between pipeline stages. The predicted theoretical IPC slowdown (relative to the baseline processor with zero interblock wire delays) for such a processor equals  $\sum_i d_i \cdot \mu_i$ , where  $d_i$  represents each wire delay and  $\mu_i$  represents the slope of the corresponding slowdown curve in Figure 2.2. If this hypothesis is true, detailed architectural simulations can be avoided for every floorplan that is considered. To verify this hypothesis, we simulated 10 processor configurations with random wire delays (between 0 and 4 cycles) between every pair of pipeline stages. The wire delays for these configurations are shown in Table 3.1. Figure 3.1 compares the experimental IPC slowdowns against the theoretical slowdown computed according to the slopes of the curves in Figure 2.2. The maximum and average errors were 4% and 2.1%, respectively. This minor discrepancy is partially because the slowdown curve is being represented

| Lu | able 9.1. entited path latencies for 10 random configurations |      |      |      |      |      |      |      |      |      |       |

|----|---------------------------------------------------------------|------|------|------|------|------|------|------|------|------|-------|

|    |                                                               | cfg1 | cfg2 | cfg3 | cfg4 | cfg5 | cfg6 | cfg7 | cfg8 | cfg9 | cfg10 |

|    | Dcache-IntALU                                                 | 3    | 2    | 1    | 4    | 0    | 2    | 3    | 0    | 1    | 0     |

|    | Dcache-DFPALU                                                 | 3    | 0    | 4    | 3    | 1    | 3    | 2    | 3    | 4    | 0     |

|    | FP-IntALU                                                     | 1    | 1    | 3    | 4    | 4    | 3    | 1    | 3    | 0    | 0     |

|    | Bpred-Icache                                                  | 0    | 2    | 0    | 0    | 1    | 4    | 2    | 1    | 0    | 0     |

|    | Decode-Rename                                                 | 2    | 2    | 1    | 1    | 4    | 0    | 1    | 4    | 2    | 4     |

|    | Rename-IQ                                                     | 3    | 4    | 0    | 3    | 0    | 2    | 0    | 0    | 4    | 2     |

|    | Dcache-L2                                                     | 4    | 1    | 2    | 2    | 3    | 3    | 1    | 0    | 3    | 2     |

|    | Decode-Icache                                                 | 3    | 4    | 2    | 2    | 1    | 0    | 1    | 1    | 1    | 1     |

|    | IQ-IntALU                                                     | 1    | 2    | 3    | 1    | 3    | 4    | 1    | 4    | 4    | 4     |

|    |                                                               |      |      |      |      |      |      |      |      |      |       |

Table 3.1. Critical path latencies for 10 random configurations

Figure 3.1. Additive nature of IPC degradation

as a straight line by a single slope value. We also repeated our experiments for out-of-order processor models with a range of resources and found little difference in the relative slopes of each slowdown curve.

By applying the floorplanning algorithm described, we are able to generate floorplans that reduce delays due to on-chip wires. Comparing such an IPC optimized floorplan with an unrealistic perfect floorplan with zero wire delays gives an estimate of the penalty due to wire delays in a processor. In the next section, we will see how much 3D layouts help in eliminating this penalty.

## 3.2 Optimizing 3D Floorplans

Three dimensional integrated circuits (3D ICs) [40, 41] offer an attractive opportunity to overcome the barriers of interconnect scaling. In a 3D circuit, several device layers are stacked together either in a face-to-face, face-to-back or back-to-back bonding. Vertical interconnects called as *interdie vias* or *d2d vias* are tunneled through silicon to provide direct communication paths between the various dies. An important benefit of 3D chips over a conventional 2D design is reduction of interconnect lengths. Other advantages are higher package density, smaller footprint, higher performance and lower interconnect power due to shorter overall wire lengths, and support for mixed technology chips.

The HotFloorplan [6] tool from Virginia is used to generate 2D floorplans. For each floorplan, the tool is allowed to move/rotate blocks and vary their aspect ratios, while attempting to minimize the objective function. We also extended the tool to generate 3D floorplans with a two phase approach similar to that described in [42]. The floorplan is represented as a series of *units/operands* (blocks in the floorplan) and *cuts/operators* (relative arrangement of blocks), referred to as a Normalized Polish Expression (NPE) [43]. Wong et al. [43] prove that a floorplan with n basic blocks can be represented as a unique NPE of size 2n - 1. The balloting property of an NPE ensures that any point in the NPE there are at least as many units as the number of cuts and therefore allows for the reconstruction of a valid floorplan. The design space can be explored by applying the following three operations. As long as the balloting property holds, these operations will result in a valid floorplan: (i) swap adjacent operands, (ii) change the relative arrangement of blocks (i.e., complement the operators in NPE), and (iii) swap adjacent operator and operand. This is repeatedly performed as part of a simulated annealing process until a satisfactory value for the cost function is obtained.

For the 3D floorplan, the above basic algorithm is extended with additional moves proposed by Hung et al. [42] and is implemented as a two phase algorithm. In the first phase, two *move* functions are introduced in addition to the three described in [43] – interlayer move (move a block from one die to another) and interlayer swap (swap two blocks between dies) – while still maintaining NPEs and satisfying the balloting property. The purpose of the first phase is two fold: (i) minimize the area footprint ( $area_{tot}$ ) of both the layers and the difference in the areas of each layer ( $area_{diff}$ ), and (ii) move the delay sensitive blocks between layers to reduce wire delays between them. The cost function used for this phase is (the equation parameters are clarified in Table 3.2):

$cost_{phaseI} = \alpha_A \times area_{tot} + \alpha_{wl} \times \sum_i l_i \cdot w_i + \alpha_d \times area_{diff}$

The first phase results in two die floorplans having similar dimensions that serve as inputs to the second phase. In the second phase, no interdie moves or swaps are allowed. This phase tries to minimize (i) lateral heat dissipation among units, (ii) total power density of all pairs of overlapping units, (iii) wire delays among units, and (iv) total area of each die using the three basic within-die moves as described in [43]. The cost function used for this stage is:

$$cost_{phaseII} = \alpha_A \times area_{tot} + \alpha_{wl} \times \sum_i l_i \cdot w_i + \alpha_d \times area_{diff} + \alpha_{wh} \times \sum_{i,j} A_{olap}(i,j) \times (pd_i + pd_j) + \alpha_{lh} \times \sum_{i_1,i_2} sharedlen(i_1,i_2) \times (pd_{i_1} + pd_{i_2})$$

At the end of the second phase, we obtain floorplans for two layers with favorable thermal and wire delay properties. Finally, the L2 is wrapped around the two dies in a proportion that equalizes their area.

| Parameter                                                                       | Description                                                                                                                                                   | Associated<br>Weight | Value of<br>Weight |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|

| $area_{tot}$                                                                    | Total area of both dies                                                                                                                                       | $\alpha_{tot}$       | 0.05               |

| $area_{diff}$                                                                   | Area difference between dies                                                                                                                                  | $\alpha_{diff}$      | 4e5                |

| $\sum_i l_i.w_i$                                                                | Total Wire length/delay<br>$l_i$ - length of wire $i$<br>$w_i$ - number of bits being<br>transferred on wire $i$                                              | $lpha_{wl}$          | 0.4                |

| $\begin{array}{c} \sum_{i,j} A_{olap}(i,j) \times \\ (pd_i + pd_j) \end{array}$ | Power density of overlapping units<br>$A_{olap}(i, j)$ - overlapping area<br>between units <i>i</i> and <i>j</i> ,<br>$pd_i$ - power density of unit <i>i</i> | $lpha_{vh}$          | 0.5                |

| $\sum_{\substack{i_1,i_2 \\ \times (pd_{i_1} + pd_{i_2})}} sharedlen(i_1,i_2)$  | Lateral heat dissipation factor<br>$sharedlen(i_1, i_2)$ - shared length<br>between units $i_1$ and $i_2$                                                     | $lpha_{lh}$          | 5e - 5             |

Table 3.2. 3D floorplanner cost function parameters

### 3.3 Floorplanning Results

In this section we will discuss the methodology of our floorplanning algorithms and present detailed results for the optimal 2D and 3D floorplans obtained. Throughout this section we only deal with optimal single core floorplans and estimate the impact of wire delays within an uniprocessor core.

#### 3.3.1 Methodology

HotSpot-3.0's grid model is used to determine the transient temperatures of the 2D and 3D layouts. The power traces to HotSpot are obtained using the Wattch power model for 90nm technology. Heat dissipation on interconnects is also modeled by attributing interconnect power to its connected units in the ratio of their areas, As discussed earlier, we also extend HotFloorplan [6] to evaluate 3D layouts and to include the  $IPC\_penalty$  factor while generating optimal floorplans. The microprocessor model fed to HotFloorplan is very similar to the Alpha 21264 [32] – the same microarchitectural blocks and relative sizes are assumed. The slopes of the slowdown curves in Figure 2.2 are used to compute the  $IPC\_penalty$  weights for each set of wires. These weights are listed in Table 3.3 along with the corresponding cycles required for each communication (for two different processor models).

To estimate the performance of each floorplan, we determine the distances between the centers of interacting blocks and compute wire latencies for two different types of wires – fast global wires on the 8X metal plane and semiglobal wires on the 4X plane. The processor is assumed to have four types of metal layers, 1X, 2X, 4X, and 8X, with the notation denoting the relative dimensions of minimum width wires [44]. 1X and 2X planes are used for local wiring within circuit blocks. These latencies are converted to cycles for two clock speed assumptions – 2 GHz and 4 GHz. The data in Table 3.3 show the corresponding cycles required for each communication in the most wire constrained model (wires are implemented on the slower 4X metal plane and a fast clock speed of 4 GHz is assumed) and the least wire constrained model (wires are implemented on the faster 8X plane and a clock speed of 2 GHz is assumed) for the optimal 2D floorplan. If the wire delay between blocks is less than 1 FO4, we assume that the delay can be somehow absorbed in

| ſ | Critical loop   | Weight | Delay for optimal    | Delay for optimal  |

|---|-----------------|--------|----------------------|--------------------|

|   | 1               | 0      | 2D floorplan         | 3D floorplan       |

|   |                 |        | 4X wires $(4  GHz)/$ | 4X wires (4 GHz) / |

|   |                 |        | 8X wires (2 GHz)     | 8X wires (2 GHz)   |

| ĺ | DCACHE-INTALU   | 18     | 1/1                  | 0/0                |

|   | DCACHE-FPALU    | 1      | 3/1                  | 1/1                |

|   | BPRED-ICACHE    | 2      | 1/1                  | 1/1                |

|   | IQ-INTALU       | 6      | 1/1                  | 1/1                |

|   | FP-INTALU       | 1      | 2/1                  | 1/1                |

|   | DECODE-RENAME   | 2      | 1/1                  | 1/1                |

|   | RENAME-IQ       | 4      | 1/1                  | 1/1                |

|   | DCACHE-L2       | 2      | 1/1                  | 1/1                |

|   | DECODE - ICACHE | 2      | 2/1                  | 1/1                |

**Table 3.3**. Weights for the different pairs of blocks and the corresponding wire delays for the least constrained and most constrained models

the previous pipeline stage and no additional cycles of wire delay are introduced. The L2 latency is determined by adding the wire delay between the L1 cache and the nearest L2 bank to the 30 cycle L2 access time. This way, we are able to obtain optimal floorplans for both the 2D and 3D case and evaluate their performance relative to a baseline that has no wire delays.

The average power values for each microarchitectural block are derived from the Wattch power model [45] for 90 nm technology and this is used by HotFloorplan to estimate temperatures within each candidate floorplan. Wattch's default leakage model is employed, where a certain fraction of a structure's peak power is dissipated in every idle cycle. The leakage value is not a function of the operating temperature, thus under underestimating the power consumed by hot units. As we later show, even with this advantage, the hotter 3D architectures are unable to significantly outperform the cooler 2D architectures. Since we are preserving the 2D implementation for each circuit block and not folding them across multiple dies, Wattch's default power models for each block can be employed. HotFloorplan uses Hotspot-3.0's [46] grid model with a  $50 \times 50$  grid resolution. Hotspot's default heat sink model and a starting ambient temperature of  $45^{\circ}$ C is assumed for all temperature experiments throughout the paper.

For 3D floorplans, each die is modeled as two layers – the active silicon and the bulk silicon. The dies are bonded face-to-face (F2F) and the heat sink is placed

below the bottom die. A layer of thermal interface material (TIM) is modeled between the bulk silicon of the bottom die and the heat spreader [47]. The thermal parameters for the various layers of the 3D chip are listed in Table 3.4. The power consumed by data wires between pipeline stages at 90 nm is also considered [48]. Hotspot does not consider interconnect power for thermal modeling. Hence, consistent with other recent evaluations [49], interconnect power is attributed to the units that they connect in proportion to their respective areas. Similar to the methodology in [27], the reduction in area footprint from 3D is assumed to cause a proportional reduction in clock distribution power.

## 3.3.2 Comparison of Optimal 2D and 3D Floorplans

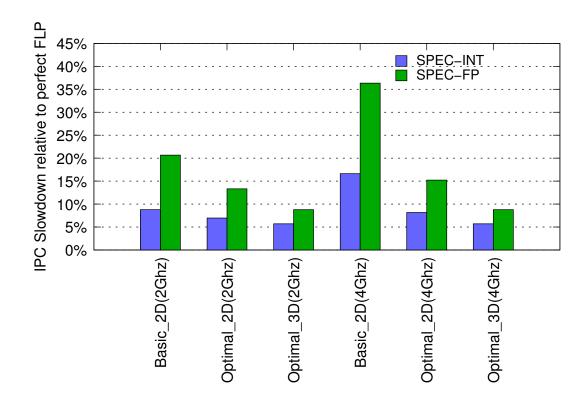

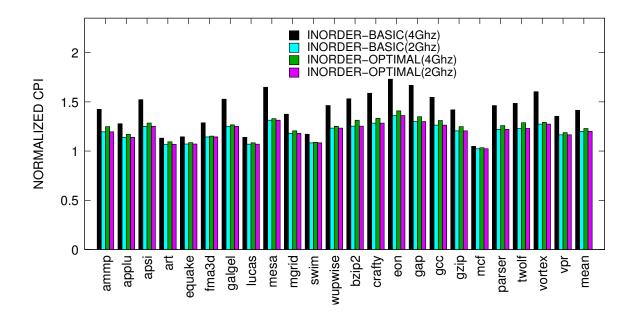

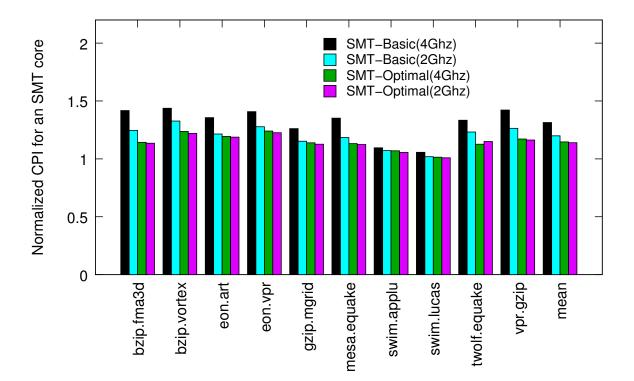

Figure 3.2 and Figure 3.3 illustrate the optimal 2D and 3D floorplans derived from our methodology respectively. The 2D floorplan obtained is based only on weights derived from the single thread (OoO) slowdown curve. The performance of these floorplans along with that of a floorplan generated by a basic wire delay incognizant floorplanner is shown in Figure 3.4. The figure plots the average slowdown of SPEC-INT and SPEC-FP benchmarks with respect to a perfect floorplan with no wire delays for the most and least wire constrained models.

| - Horman moder parameters                     |                        |  |  |  |  |

|-----------------------------------------------|------------------------|--|--|--|--|

| Bulk Si Thickness die1(next to heatsink)      | $750 \mu m$            |  |  |  |  |

| Bulk Si Thickness die2 (stacked die)          | $20 \mu m$             |  |  |  |  |

| Active Layer Thickness                        | $1 \mu { m m}$         |  |  |  |  |

| Cu Metal Layer Thickness                      | $12 \mu { m m}$        |  |  |  |  |

| D2D via Thickness                             | $5\mu \mathrm{m}$      |  |  |  |  |

| Si Resistivity                                | $0.01 \ (mK)/W$        |  |  |  |  |

| Cu Resistivity                                | 0.0833(mK)/W           |  |  |  |  |

| D2D via Resistivity (accounts for air         | $0.0166 \ (mK)/W$      |  |  |  |  |

| cavities and die to die interconnect density) | · · · · · ·            |  |  |  |  |

| HotSpot Grid Resolution                       | 50x50                  |  |  |  |  |

| Ambient temperature                           | $45^{\circ}\mathrm{C}$ |  |  |  |  |

Table 3.4.

Thermal model parameters

Figure 3.2. Optimal 2D floorplan

Figure 3.3. Optimal 3D floorplan

Figure 3.4. Comparison of basic, optimal 2D and optimal 3D floorplans

Based on these floorplans, it was observed that the optimal 2D floorplan enabled a performance improvement of 16.5% over the basic 2D floorplan. The IPC-aware 3D floorplan further achieves a performance improvement of 4%. Hence 3D stacking does not dramatically reduce critical latencies for an aggressive OoO processor.